AI-powered DRC analysis clusters billions of verification errors into actionable groups, speeding debug and improving collaboration in chip design.

AI-Powered Chip Verification: Fix DRC Bottlenecks Fast

A modern chip project can generate millions to billions of design rule checking (DRC) results—and that’s not a sign your team is failing. It’s a sign the verification workflow is stuck in an older reality: one where humans are expected to triage machine-scale data with spreadsheets, screenshots, and tribal knowledge.

Here’s the stance I’ll take: physical verification isn’t “just a late-stage checklist” anymore. It’s an industrial-scale data problem, and it needs the same kind of human-AI collaboration we’re seeing across manufacturing robotics, logistics automation, and clinical imaging. When verification stays manual, the bottleneck doesn’t merely slow tapeout—it quietly forces teams to make worse tradeoffs under schedule pressure.

This post is part of our “Artificial Intelligence & Robotics: Transforming Industries Worldwide” series, and chip verification is a perfect example of the broader pattern: AI doesn’t replace experts; it turns expert judgment into scalable systems.

Why physical verification became the slowest step

Answer first: Physical verification became a bottleneck because chip layouts grew multi-layered and context-dependent, while DRC outputs grew too large for human triage.

DRC exists for a simple reason: you can’t manufacture what you can’t reliably build. Foundries specify thousands of constraints—minimum widths, spacing, via overlap rules, multi-patterning limitations, density constraints, and process-specific quirks. The painful part is that many modern rules are contextual: whether something is “legal” can depend on nearby geometry, layer interactions, and sometimes features that aren’t even close on the die.

Meanwhile, chip complexity has moved in multiple directions at once:

- More layers and tighter geometries (shrinking features, tighter tolerances)

- Heterogeneous integration (logic + memory + analog blocks living side-by-side)

- Advanced packaging and 3D stacking (more interfaces, more constraints)

- Aggressive schedules (market windows don’t wait)

The result is predictable: teams run full-chip DRC late, see a wall of violations, and then burn weeks figuring out what’s real, what’s systemic, and what’s “expected noise.”

The “millions of violations” problem isn’t the real problem

Answer first: The real problem isn’t volume—it’s that the results don’t naturally organize into actions.

When DRC is done late, violations are expensive. When teams “shift left” (run earlier at block/cell level), violations are cheaper to fix—but the dataset can become astronomical because the design is still “dirty.” That’s where traditional flows break:

- Engineers cap errors per rule to keep tools responsive

- Teams email screenshots and partial databases

- Debug knowledge lives in a few senior people’s heads

Those workarounds don’t scale. They also hide chip-wide patterns that matter most—like a repeated via enclosure mistake propagated by a template, or a density rule violation caused by one global floorplan decision.

Shift-left verification: the right idea that creates new pain

Answer first: Shift-left DRC is essential, but it demands AI-driven prioritization or teams drown in early-stage noise.

“Shift left” and concurrent build methods are the verification equivalent of modern industrial operations: instead of doing everything sequentially, you run checks continuously while design evolves. It’s the same logic behind robotics-enabled production lines that inspect quality during assembly rather than after the last bolt is tightened.

The payoff is real:

- Fixes happen when layout changes are small and localized

- Fewer end-stage surprises

- Better predictability for tapeout readiness

But early DRC also creates a new operational reality: you’re now running analyses on designs that are intentionally incomplete. Without intelligent triage, you get more data than decision-making capacity.

Here’s what I’ve seen work conceptually (even beyond the chip world): if you can’t rank, cluster, and route issues to owners, you don’t have a workflow—you have a flood.

What “good” looks like: treating verification results like a production system

Answer first: The winning teams treat DRC outputs as a shared, living dataset, not a static report.

In robotics and AI-powered manufacturing, inspection results become part of a feedback loop: detect → categorize → assign → correct → learn. Chip verification can work the same way if results are:

- Collaborative: assign ownership, annotate, and share exact states

- Structured: grouped by root cause, not just by rule number

- Traceable: reproducible debug paths that survive handoffs

That’s the bridge from “EDA tool output” to “industrial process control.”

Where AI changes the verification math

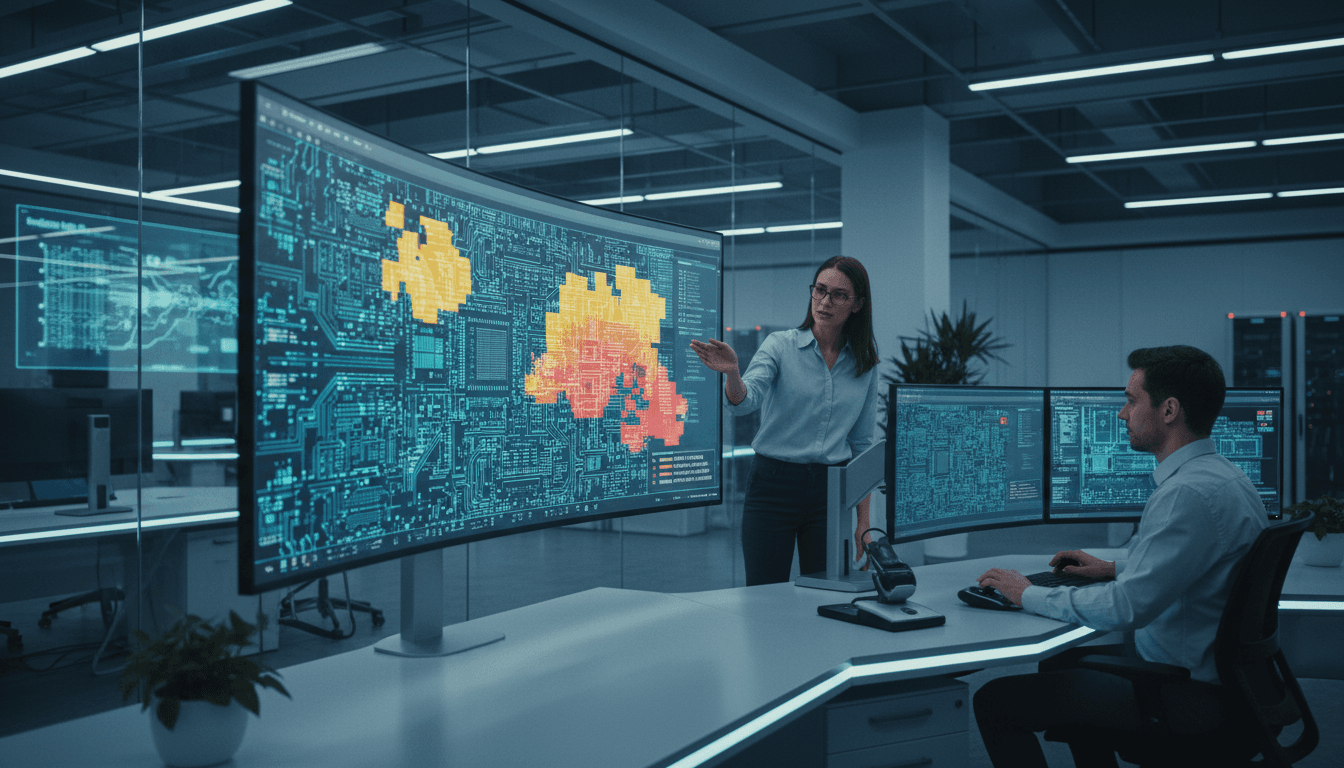

Answer first: AI improves DRC analysis by turning billions of raw markers into clusters that map to root causes, cutting manual investigation time dramatically.

The RSS source (sponsored by Siemens) highlights a key shift: modern AI systems can process enormous DRC datasets and identify patterns humans simply can’t see fast enough. The most practical framing isn’t “AI finds errors.” DRC already finds errors. The practical framing is:

AI turns error lists into a prioritized to-do list.

That typically involves a few AI/ML techniques working together:

- Clustering: group geometrically and contextually similar violations

- Computer vision-like feature extraction: treat layout/markers as visual patterns

- Outlier detection: find unusual regions that basic filters miss

- Guided summaries: explain what changed, what’s trending worse, and what’s stable

Why clustering beats brute-force filtering

Answer first: Filters hide information; clustering organizes it.

A filter might reduce 600 million markers to 50,000. That’s smaller—but it still doesn’t tell you whether those 50,000 come from one systematic root cause or 5,000 unrelated issues.

Clustering flips the workflow:

- Group similar errors across the die

- Inspect a small number of representative examples

- Fix the underlying pattern (template, rule interaction, routing strategy)

- Watch hundreds or millions of markers disappear

This is the same reason predictive maintenance systems in factories don’t just show “all vibration alarms.” They group signals into failure modes and probable causes.

A concrete example: AI-driven DRC analysis and collaboration

Answer first: Tools like Siemens’ Calibre Vision AI show what AI-assisted DRC looks like when it’s built for scale, speed, and team workflows.

From the provided RSS summary, Calibre Vision AI focuses on two outcomes that matter most in real projects:

- Time-to-insight: loading and visualizing massive results quickly

- Root-cause debug: clustering billions of errors into a manageable set of groups

The article cites several specific performance examples:

- A case where a results file that took 350 minutes in a traditional flow took 31 minutes with the Vision AI flow.

- A scenario where legacy tooling would require slogging through 3,400 checks and 600 million errors, while AI clustering reduced investigation to 381 groups.

- Another case (described in the RSS summary) where 3.2 billion errors across 380+ rule checks were clustered into 17 groups in about five minutes.

Those numbers matter because they describe a workflow change, not just a speedup. When you reduce work from “scan millions of markers” to “review a few hundred groups,” you’ve effectively expanded the capacity of your verification team without hiring.

Collaboration features are not “nice to have” anymore

Answer first: At advanced nodes, collaboration is part of verification accuracy.

The RSS summary calls out dynamic bookmarks, shared UI states, annotations, and ownership assignment. That might sound like convenience—until you’ve lived through late-stage tapeout pressure.

When teams pass screenshots around, three bad things happen:

- The context gets lost (layers on/off, exact zoom, filters applied)

- Two engineers debug the same thing unknowingly

- Decisions aren’t traceable (“Why did we waive this?”)

Treating DRC results as a shared workspace—where the state of analysis is portable—mirrors how modern robotics operations share live dashboards across shifts and sites. The workflow becomes repeatable, auditable, and faster.

The hidden win: closing the expertise gap

Answer first: AI-assisted verification helps less-experienced engineers perform at a higher level by standardizing analysis paths that used to require years of intuition.

Chip verification has an uncomfortable truth: many teams depend on a small number of senior experts who can look at a pattern of violations and say, “That’s a template issue,” or “That’s a routing strategy problem.” Workforce constraints make that dependency risky.

AI clustering and guided analysis can encode part of that pattern recognition into the tool:

- New engineers can start with meaningful groups instead of raw noise

- Senior engineers spend time on design decisions, not data wrangling

- Teams get more consistent triage across blocks and sites

This aligns directly with the broader theme of our series: human-AI collaboration scales expertise in the same way collaborative robots scale production.

Practical checklist: how to adopt AI in chip verification (without chaos)

Answer first: Start by modernizing the workflow around ownership, data hygiene, and measurable outcomes—then layer in AI.

If you’re evaluating AI-driven DRC analysis (whether Siemens’ approach or another), I’d focus on these practical steps:

- Define “actionable output.” Decide what engineers should receive: clusters, ranked hot spots, regression deltas, or all three.

- Instrument your baseline. Track current load times, time-to-first-root-cause, and average engineer-hours per DRC cycle.

- Pilot on a painful block. Pick the block that consistently explodes late in the schedule—where the ROI will be obvious.

- Standardize collaboration. Require annotations, ownership assignment, and consistent handoff artifacts (not screenshots).

- Treat clustering as a feedback loop. When a cluster maps to a known root cause, document it and reuse that knowledge.

If AI doesn’t reduce one of these measurable burdens—load time, triage time, or rework—it’s not helping.

What this signals for AI & robotics across industries

Answer first: AI-powered chip verification is a template for how AI transforms technical industries: it turns complex diagnostics into operational systems.

Semiconductors sit upstream of nearly every industry featured in this series—robotics, automotive, healthcare devices, energy, and telecom. When verification drags, everything downstream feels it.

The broader lesson is portable:

- In factories, AI groups inspection defects into failure modes.

- In logistics, AI groups delays into root causes (weather, capacity, routing, labor).

- In chip design, AI groups DRC violations into clusters you can actually fix.

Same move, different domain: convert overwhelming signals into decisions.

Next steps: turning DRC from a crisis into a cadence

AI in chip verification is most valuable when it changes the rhythm of work: fewer late-stage fire drills, more continuous confidence. If your team is already doing shift-left verification but still drowning in “dirty” datasets, that’s a strong signal the bottleneck has moved from compute to cognition.

If you’re building a roadmap for 2026 programs, I’d make one recommendation: treat verification data as a first-class product. Organize it, share it, and use AI to turn it into repeatable actions.

Where would your organization feel the impact first—shorter tapeout cycles, higher yield confidence, or fewer late-stage surprises?